联系人:张经理

移动电话:15862538293

电话:0512-62650893

传真:0512-62650891

邮箱:sunny@ptitech.com.cn

网址:http://www.ptitech.com.cn

地址:苏州工业园区和顺路29号

电路板测试之边界扫描技术(Boundary Scan)

可测性设计

• 由于线路越来越复杂,大型的IC要做全功能测试的可能性越来越低(因全功能检查时间太长)

• 在生产的角度来看:关心工艺制程问题要比工程问题本身更为重要

• 产品有不良(错误)或不乎指标,工程修改

• IC的开短路,IC的质量,是生产最关心的问题。

• 在测试IC脚之间的短路,只需要在IC每一跟脚下一根针便能检测IC的浮接只通过保护二极管,eScan,TestJet等方法去解决此等测试为非带电测试,稳定性,及可测范围都受到一定影响

• 为有一些IC另外的解决方案Nand Tree与Bounday Scan

• 加快测试解决方案客制化的进程

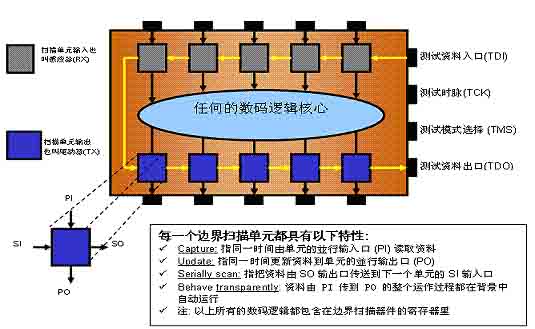

边界扫描结构

基本信号:TDI, TDO ,TMS ,TCK ,TRST*

JTAG 能测什么?

Infrastructure Tests

• 扫描链连接测试

• TAP 控制器测试

• 漏件

• 错件

Interconnection Tests

• Stuck 0/1

• 开短路

• 连接器

Clustering

• 功能测试

• 记忆体测试

Functional Tests

• 同步罗揖

• 非同步罗揖

边界扫描测试目标

• BS 元件与BS元件之间试其相连的元件之生

产工艺缺陷

• 静电做成的损害

• 机械故障(脚变形,错件, …)

• 热故障(空焊, 连焊..)

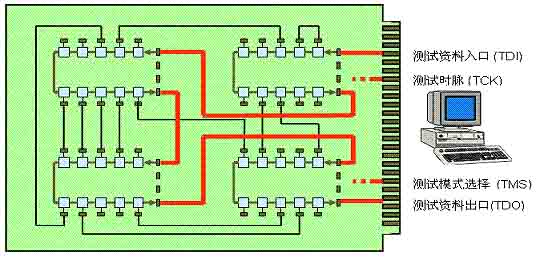

JTAG 完整结构